## SiC rapid thermal carbonization of the (111)Si semiconductor-on-insulator structure and subsequent metalorganic chemical vapor deposition of GaN

A. J. Steckl<sup>a)</sup> and J. Devrajan University of Cincinnati, Cincinnati, Ohio 45221-0030

C. Tran and R. A. Stall

EMCORE Corporation, Somerset, New Jersey 08873

(Received 12 June 1996; accepted for publication 26 July 1996)

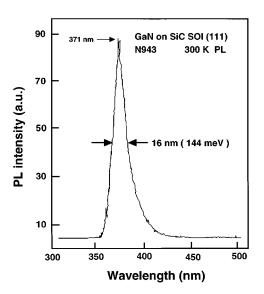

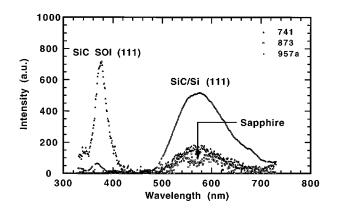

Si (111) semiconductor-on-insulator (SOI) structures have been converted to SiC by carbonization of the thin (<100 nm) Si layer using rapid thermal chemical vapor deposition with mixtures of propane and H<sub>2</sub> at atmospheric pressure. Carbonization temperatures around 1225–1250 °C produced SiC films with optimum structural properties. X-ray diffraction (XRD) reveals a single SiC peak at  $2\theta$ =35.7° corresponding to the (111) reflection, with an uncorrected full width at half-maximum (FWHM) of ~0.24°. Infrared spectroscopy of SiC SOI structures obtained under optimum carbonization conditions exhibited a sharp absorbtion peak produced by the Si–C bond at 795 cm<sup>-1</sup>, with FWHM=22–25 cm<sup>-1</sup>. Metalorganic chemical vapor deposition growth of GaN on the (111) SiC SOI was carried out with trimethylgallium and NH<sub>3</sub> precursors at 1000 °C. XRD indicates highly oriented hexagonal GaN, with FWHM of the (0002) peak of ~0.15°. The 300 °K photoluminescence (PL) spectrum of GaN films exhibits a strong near band-edge peak (at  $\lambda_p$ ~371 nm, with FWHM=100–150 meV) and weak yellow emission. Under low power excitation, the 370 nm PL emission from the GaN/SiC SOI structure displays an emission intensity ~10× higher than that of equivalent GaN films grown on sapphire. © *1996 American Institute of Physics*. [S0003-6951(96)01241-7]

SiC is a wide band-gap semiconductor (WBGS) under development mainly for applications<sup>1,2</sup> requiring operation at high temperature, high power, or high frequency. The SiC semiconductor-on-insulator (SOI) structure represents an exciting approach for the development of large area, low cost SiC. The starting point for SiC SOI is a silicon SOI wafer consisting of a normal Si substrate, an oxide layer and a thin Si device layer. The Si SOI structure is produced either by thermal bonding and etch back of two Si wafers or by oxygen ion implantation. The rapid development of Si SOI technology is currently driven by the needs of low power, low voltage applications.<sup>3</sup> In addition, it is expected that SOI will also play a major role in future generations of Si circuits. As a result of the opportunities and pressures of this highly competitive environment, commercial suppliers are pursuing the goal of developing Si SOI technology comparable to Si substrates in terms of wafer diameter, quality, and cost. In turn, the SiC SOI approach can take advantage of the increasing availability of starting SOI material.

The SiC SOI structure can be utilized for the fabrication of SiC devices or it can serve as a substrate for the thin film growth of other materials. In principle, the SiC SOI approach is superior to growth of SiC directly on a Si wafer. This is due to the fact that the Si device layer in the SOI structure can be made quite thin, enabling the complete conversion of Si to SiC. The presence of a finite amount of Si in the SOI structure minimizes the formation of voids typically found after the carbonization of conventional Si substrates. The relatively plastic oxide layer is beneficial in absorbing stress and dislocations. In addition, the electrical advantages of the Si SOI structure (e.g., absence of latch up, reduced parasitic capacitance, shallow junctions) can hopefully be transferred to SiC SOI devices.

We have previously reported<sup>4</sup> the feasibility of forming SiC SOI structures using the process of direct carbonization of Si (100) by reaction with propane, followed by growth with silacyclobutane. In this letter we report on the formation of (111) SiC SOI structures using carbonization and the subsequent growth of GaN films by metalorganic chemical vapor deposition (MOCVD). The recent breakthroughs in III-V nitride-based devices,<sup>5</sup> including commercial blue and multicolor light-emitting diodes and the feasibility of blue semiconductor diode lasers,<sup>6</sup> clearly indicate the rapidly accelerating development of these WBGS materials. A critical challenge for this technology is the development of a suitable substrate material (which is well lattice matched and thermally compatible with GaN), which is available with large area and at low cost. At present, GaN and related alloys are grown primarily on sapphire substrates because of their commercial availability and excellent surface preparation. Sapphire, though relatively low priced, has a very large lattice mismatch ( $\sim 16\%$ ) with wurtzite GaN. Hexagonal 6H–SiC, which has a much smaller lattice mismatch ( $\sim$ 3%), is in principle a more suitable substrate, but is available only in small diameters and is very expensive. We have, therefore, explored the fabrication of SiC SOI structures suitable as large area, low cost substrates for GaN growth.

The starting materials were Si SOI structures consisting of a thin Si (111) device layer (900–1000 Å), a 1  $\mu$ m SiO<sub>2</sub> layer, and a Si (100) substrate. The orientation of the Si (111) layer was tilted 2.4°–4° off axis. The Si SOI was

<sup>&</sup>lt;sup>a)</sup>Electronic mail: a.steckl@uc.edu

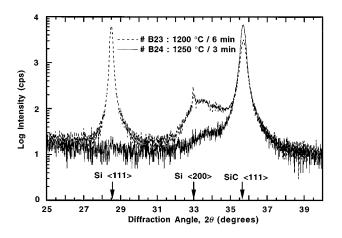

FIG. 1. Wide angular range x-ray diffraction spectra of (111) SiC SOI structures obtained by carbonization at 1200 and 1250 °C.

produced<sup>7</sup> by thermal bonding and etch back. The final step involved a specialized plasma etching process<sup>8</sup> to provide the 0.1  $\mu$ m Si device layer with high uniformity over the wafer area. Growth on the (111) plane was chosen for two reasons: (a) superior results with growth of 3C-SiC directly on (111) Si substrates were previously reported;<sup>9</sup> and (b) the (111)SiC surface, which is essentially identical to the c plane of 6H-SiC, is a better match for subsequent growth of III-N films. To prevent unnecessary exposure to high temperature, the SiC growth was carried out in a rapid thermal chemical vapor deposition reactor that easily allowed for reaction times of only a few minutes needed for complete carbonization. The reaction was performed at temperatures from 1100 to 1300 °C with mixtures of propane (5% in  $H_2$ ) and  $H_2$  at 760 Torr. The optimum carbonization temperatures were found to be in the 1225-1250 °C range. The carbonization process is described in more detail elsewhere.<sup>10,11</sup> The thickness of the SiC layer produced by carbonization was approximately equal to that of the original Si device layer. The resulting SiC SOI structures have been characterized with regard to structure by x-ray diffraction (XRD) and composition by Fourier transform infrared spectroscopy (FTIR). Shown in Fig. 1 are XRD spectra for two SiC SOI samples grown at 1200 °C for 6 min and at 1250 °C for 3 min. The structure carbonized at 1250 °C reveals a single sharp SiC peak at  $2\theta = 35.7^{\circ}$  corresponding to the (111) plane reflec-

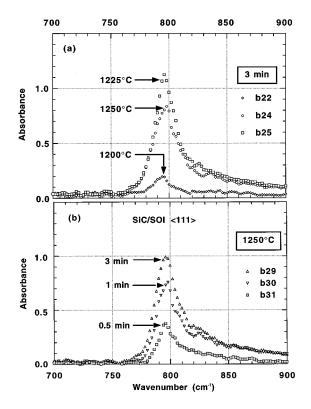

FIG. 3. Fourier transmission infrared spectra of SiC SOI structures obtained by carbonization: (a) different temperatures and fixed time (3 min); and (b) fixed temperature (1250 °C) and varying times.

tion. The sample produced at 1200 °C also exhibits the SiC  $\langle 111 \rangle$  peak and two additional contributions at  $2\theta$ =28.4° and 33°. These two peaks are identified with Si  $\langle 111 \rangle$  from the remaining Si device layer and Si  $\langle 200 \rangle$  from the Si substrate. We can conclude that the Si-to-SiC conversion rate at 1200 °C is low enough to prevent complete conversion in 6 min, whereas at 1250 °C the carbonization process is complete in 3 min or less.

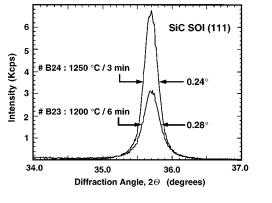

High resolution, limited range XRD scans of the SiC (111) peak of the same samples are shown in Fig. 2. The sample grown at 1200 °C exhibits a peak with an uncorrected full width at half-maximum (FWHM) of  $\sim 0.28^{\circ}$ , while the sample grown at 1250 °C has a FWHM of  $0.24^{\circ}$ . Correcting for XRD system broadening normally reduces the FWHM by about  $0.05-0.1^{\circ}$ . These XRD values obtained for the (111) SiC SOI structure are better than those previously

FIG. 2. High resolution XRD spectra of the SiC (111) peaks of SiC SOI samples carbonized at 1200 and 1250 °C.

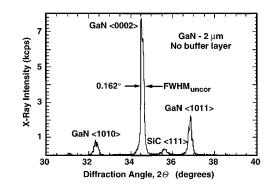

FIG. 4. X-ray diffraction spectrum of GaN/SiC SOI structure.

Appl. Phys. Lett., Vol. 69, No. 15, 7 October 1996 Downloaded¬23¬Nov¬2002¬to¬24.209.201.18.¬Redistribution¬subject¬to¬AIP¬license¬or¬copyright,¬see¬http://ojps.aip.org/aplo/aplcr.jsp

FIG. 5. Room temperature PL of GaN/SiC SOI structure obtained under high power excitation (pulsed  $N_2$  laser).

obtained<sup>4</sup> from (100) SiC SOI structures produced by the same carbonization process.

FTIR spectroscopy was utilized to determine the formation of SiC during the carbonization reaction and to obtain optimum growth conditions. The Si–C bond produces a characteristic IR absorption peak at ~795 cm<sup>-1</sup>. Absorbance spectra covering the 700–900 cm<sup>-1</sup> range are shown in Fig. 3. In Fig. 3(a) are shown spectra for structures carbonized for 3 min at temperatures ranging from 1200 to 1250 °C. At the lower end of the range only a small Si–C peak is observed, while for the 1225 and 1250 °C temperatures a significant peak is present. The FWHM of the peaks are approximately  $20-22 \text{ cm}^{-1}$ , which is an excellent range for such thin films. Keeping the carbonization temperature constant at 1250 °C, the absorption spectra of Fig. 3(b) indicate the effect of increased Si-to-SiC conversion obtained by increasing the reaction time from 0.5 to 3 min.

Metalorganic CVD growth of GaN layers on the (111) SiC SOI structures was carried out in a stainless steel, rotating disk reactor with trimethylgallium and NH<sub>3</sub> precursors. The GaN growth was performed at 1000 °C for 1 h, producing  $\sim 2 \ \mu m$  films. Experiments with GaN buffer layers grown at low temperature indicated that optimum results

FIG. 6. Room temperature PL obtained under low power excitation (cw He-Cd laser) from GaN film grown on the following substrates: (111) SiC SOI; (111) SiC/Si; sapphire.

were produced with either a very thin or no such layer. The results presented below are for GaN films grown without a buffer layer. The XRD spectrum of the GaN/SiC SOI structure shown in Fig. 4 indicates highly oriented wurtzite GaN with dominant growth orientation along the *c* axis. The uncorrected FWHM of the (0002) peak is ~0.16° or ~580 arcsec. Correcting for system broadening results in a FWHM of ~360 arcsec. The structure of GaN films grown on (111) SiC SOI structures is comparable to GaN grown on 6H–SiC substrates (for example, as reported<sup>13</sup> by Lin *et al.* to have a FWHM of ~310 arcsec) and is superior to GaN grown directly on (111) Si (reported<sup>14</sup> by Yang *et al.* to have an FWHM of 1500 arcsec).

The optical properties of the GaN layers grown on SiC SOI were investigated by photoluminescence (PL) at 300 °K. The PL spectrum of a GaN film obtained under relatively high excitation levels (using a pulsed N<sub>2</sub> laser) is shown in Fig. 5. A strong near band-edge peak at  $\lambda_p \sim 371$ nm is observed, with a FWHM corresponding to ~140–150 meV. Very weak yellow band emission was present (not shown in Fig. 4). The room temperature PL obtained under low excitation (from a cw He–Cd laser) from GaN films grown under the same conditions on the following substrates is shown in Fig. 6: (111) SiC SOI, (111) SiC/Si, and sapphire. It is interesting to observe that under these excitation conditions, by far the strongest UV emission came from the GaN/SiC SOI structure.

In summary, the fabrication of SiC SOI (111) structures by carbonization and subsequent GaN growth have been presented for the first time. The encouraging characteristics of both the SiC and GaN films indicate that this alternative approach for substrate technology should be investigated in greater detail.

The authors would like to acknowledge C. Yuan, who initiated this project first at the University of Cincinnati and then at EMCORE, and who, sadly, participated in it all too briefly. This work was partially supported by USAF Rome Lab (D. Bliss–Hanscom AFB) under Contract No. F19628-95-C-0186 and by the Office of Naval Research (M. Yoder, C. Wood) under Contract No. N00014-95-C-0302.

- <sup>1</sup>R. J. Trew, J-B. Yan, and P. M. Mock, Proc. IEEE 79, 598 (1991).

- <sup>2</sup>R. F. Davis, G. Kelner, M. Shur, J. W. Plamour, and J. A. Redmond, Proc. IEEE **79**, 677 (1991).

- <sup>3</sup>J. P. Colinge, *Silicon-on-Insulator: Materials to VLSI* (Kluwer, Dordrecht, 1991).

- <sup>4</sup>A. J. Steckl, C. Yuan, Q-Y. Tong, U. Gösele, and M. J. Loboda, J. Electrochem. Soc. **141**, L66 (1994).

- <sup>5</sup>S. N. Mohammad, A. A. Salvador, and H. Morkoç, Proc. IEEE **83**, 677 (1995).

- <sup>6</sup>S. Nakamura *et al.*, Jpn. J. Appl. Phys. **35**, L74 (1996).

- <sup>7</sup>IPEC Corp., Danbury, Connecticut.

- <sup>8</sup> P. B. Mumola, G. J. Gardopee, T. Feng, A. M. Ledger, P. J. Clopis, and P. E. Miller, Proc. Electrochem. Soc. (1993).

- <sup>9</sup>C. Yuan, A. J. Steckl, and M. J. Loboda, Appl. Phys. Lett. **64**, 3000 (1994).

- <sup>10</sup>A. J. Steckl and J. P. Li, IEEE Trans. Electron Devices **39**, 64 (1992).

- <sup>11</sup>J. P. Li and A. J. Steckl, J. Electrochem. Soc. **142**, 634 (1995).

- <sup>12</sup>C. Yuan et al., J. Electrochem. Soc. 142, 163 (1995).

- <sup>13</sup> M. E. Lin, B. Sverdlov, G. L. Zhou, and H. Morkoç, Appl. Phys. Lett. 62, 3479 (1993).

- <sup>14</sup>Z. Yang, F. Guarin, I. W. Tao, W. I. Wang, and S. S. Iyer, J. Vac. Sci. Technol. B **137**, 789 (1995).

2266 Appl. Phys. Lett., Vol. 69, No. 15, 7 October 1996

Downloaded¬23¬Nov¬2002¬to¬24.209.201.18.¬Redistribution¬subject¬to¬AIP¬license¬or¬copyright,¬see¬http://ojps.aip.org/aplo/aplcr.jsp